1. [20%] Consider a MIPS processor with an additional floating point unit. Assume functional unit delays in the processor are as follows: memory (2 ns), ALU and adders (2 ns), register file access (1 ns), FPU add (8 ns), FPU multiply (16 ns), and the remaining units (0 ns). Also assume instruction mix are as follows: load (31%), stores (21%), R-format instructions (27%), branches (5%), jumps (2%), FP adds and subtracts (7%), and FP multiplies and divides (7%).

(a) What is the delay in nanosecond to execute a load, store, R-format, branch, jump, FP add/subtract, and FP multiply/divide instruction in a single MIPS design?

(b) What is the averaged delay in nanosecond to execute a load, store, R-format, branch, jump, FP add/subtract, and FP multiply/divide instruction in a multicycle MIPS design?

參考解答:(a) 20 ns (b) 67.84 ns

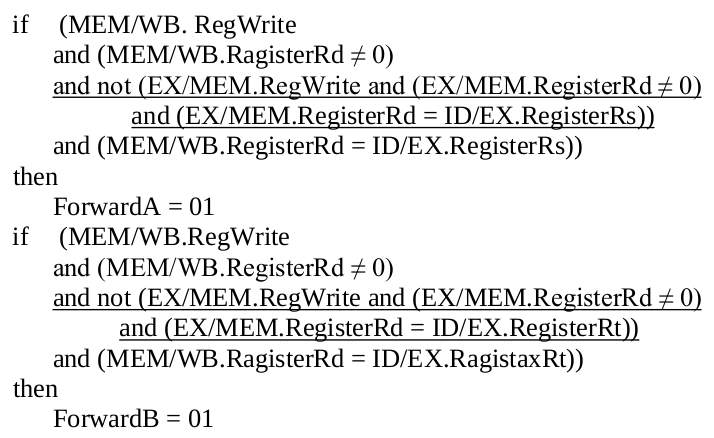

2. [15%] Consider a pipelined processor that executes the MIPS code shown in Figure 1 using the logic of hazard detection and data forwarding unit shown in Figure 2. If the MIPS code cannot be executed correctly, then how do we revise the logic shown in Figure 2 such that the code can be correctly executed?

Figure 1: The MIPS code:

add $1, $1, $5

add $1, $1, $6

add $1, $1, $7Figure 2: The logic of hazard detection and data forwarding unit:

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd != 0)

and (EXE/MEM.RegisterRd = ID/EX.RegisterRs)

and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

then ForwardA = 01

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd != 0)

and (EXE/MEM.RegisterRd = ID/EX.RegisterRt)

and (MEM/WB.RegisterRd = ID/EX.RegisterRt))

then ForwardB = 01參考解答:

The logic should be revised as follows:

3. [10%] What is the biased single precision IEEE 754 floating point format of 0.9375? What is the purpose to bias the exponent of the floating point numbers?

參考解答:

(1) 0011 1111 0111 0000 0000 0000 0000 0000

(2) Keeping the exponent field in positive numbers can speed up the comparison process.

4. [5%] Which of the following techniques can resolve control hazards?

(a) Branch prediction

(b) Stall

(c) Delayed branch

參考解答:a, b, c.

5. [15%] In a demand-paging system using a system-wide inverted page table,

(a) why are per-process page table still required?

(b) when is a per-process page table accessed?

參考解答:

(a) Because inverted page table no longer contains complete information about the logical address space of a process, and that information is required if a referenced page is not in memory.

(b) When page-fault occurs, we will access the per-process page table.

6. [15%] Which of the following may reduce TLB misses? Explain your answers briefly.

(a) increase the level of paging

(b) use pre-paging

(c) decrease the page size

參考解答:(a) F (b) T (c) F

7. [10%] In Linux, a process cannot hold a spinlock while attempting to acquire a semaphore. Please explain why this policy is in place.

參考解答:To break the hold-and-wait necessary condition for deadlocks, without the hold-and-wait condition, the system is deadlock-free.

8. [10%] Please explain why UNIX inodes support large files while allowing fast accesses to small files.

參考解答:In UNIX file system, they use inode structure where the first 12 entries are pointed directly to the data blocks and the next 3 entries are 1-level indirect, 2-level indirect and 3-level indirect, respectively. Where 1-level indirect entry points to another block with full of entries and then is the data block. So UNIX inode structure can easily support small files and large files at the same time.

試題(pdf):連結

有任何問題,或想要完整解釋的,歡迎在下方留言唷!

Lin

想請問第一題是如何計算的

mt

(a)可以發現FP mul/div所需的時間為2 + 1 + 16 + 0 + 1 = 20ns,其他指令都小於20ns,所以取20ns為delay。

(b)因為是multicycle MIPS design,所以取16ns為cycle time,則可以得到(5 * 0.31 + 4 * 0.21 + 4 * 0.27 + 3 * 0.05 + 3 * 0.02 + 4 * 0.07 + 4 * 0.07) * 16ns = 67.84ns。

Lin

非常感謝!