1. [7%] Determine whether each of the following statements is true (T) or false (F).

(1) Program execution time reduces when the clock rate increases.

(2) Program execution time reduces when the CPI increases.

(3) Program execution time reduces when the instruction count (IC) increases.

(4) Suppose the floating point instruction are enhanced and can run 10 times faster. If the execution time before the floating point enhancement is 80 seconds and three-fourth of the execution time is spent executing floating-point instructions, the overall speed up is at least 3.

(5) Suppose the floating point instructions are enhanced and can run 20 times faster. If the execution time before the floating point enhancement is 80 seconds and one-half of the execution time is spent executing floating-point instruction, the overall speed up is at least 2.

參考解答:(1) T (2) F (3) F (4) T (5) F

2. [7%] Determine whether each of the following statements is true (T) or false (F)

(1) R-type and I-type MIPS instruction can be distinguished by the opcode of an instruction.

(2) Base addressing mode is used by I-format instructions

(3) PC-relative addressing is used by J-format

(4) Suppose the program counter (PC) is at address 0x0000 0000. It is possible to use one single branch-on-equal(beq) MIPS instruction to get to address 0x0003 0000

(5) Suppose the program counter (PC) is at address 0x0000 0000, it is possible to use the jump MIPS instruction to get to 0xFFFF FFB0

參考解答:(1) T (2) T (3) F (4) F (5) F

3. [6%] The following descriptions are about IEEE 754 single precision float point format. Determine whether each of the following statements is true (T) or false (F)?

(1) The floating point format has 1 sign bit, 8 exponent bits, and 23 fraction bits.

(2) The smallest positive number it can represent is 0000 0001 0000 0000 0000 0000 0000 0000$_2$

(3) The result of “Divide 0 by 0” is 0111 1111 1000 0000 0000 0000 0000 0000$_2$

(4) To improve the accuracy of the results, IEEE 754 has one extra bit for rounding.

(5) $0.75_{10}$ is represented by 1011 1111 0100 0000 0000 0000 0000 0000$_2$

參考解答:(1) T (2) F (3) F (4) F (5) F

4. [10%]

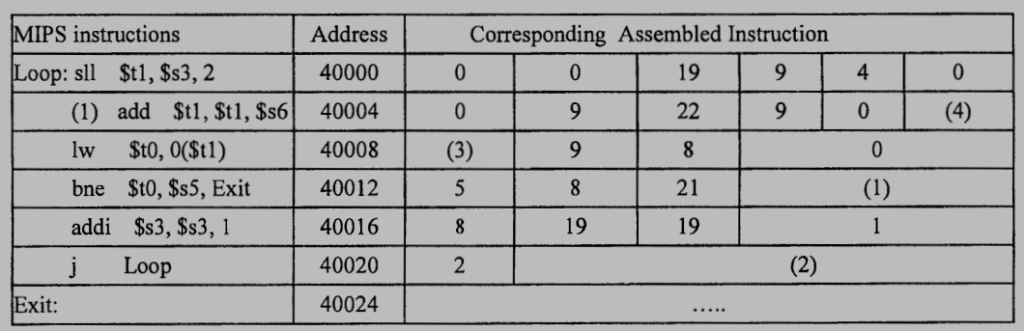

Refer to the above table and Figure 1. The right side of the above table is assembled instructions of the MIPS instructions in the left side. The starting address of the loop is 40000$_{10}$ in memory. What are the values of (1), (2), (3) and (4)? Express your answers in decimal numbers.

參考解答:(1) 2 (2) 10000 (3) 35 (4) 32

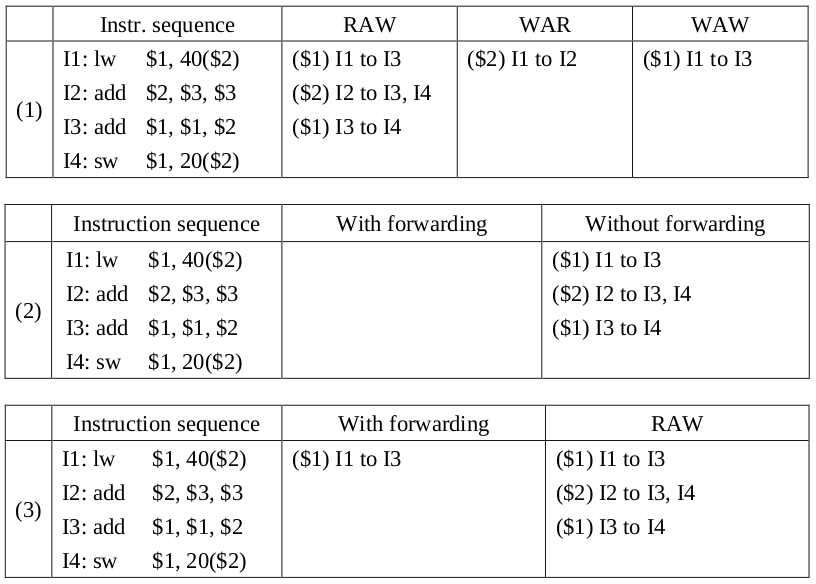

5. [15%] Refer the following instruction sequence:

lw $1, 40($2)

add $2, $3, $3

add $1, $1, $2

sw $1, 20($2)(1) Find all data dependencies in this instruction sequence.

(2) Find all hazards in this instruction sequence for a 5-stage pipeline with and without forwarding.

(3) To reduce the clock cycle time, we are considering a split of the MEM stage into two stages. Repeat (2) for this 6-stage pipeline.

參考解答:

6. Suppose that in 1000 memory references there are 50 misses in the first-level cache, 20 misses in the second-level cache, and 5 misses in the third-level cache. Assume the miss penalty from the L3 cache to memory is 100 clock cycle, the hit time of the L3 cache is 10 clocks, the hit time of the L2 cache is 4 clocks, the hit time of L1 is 1 clock cycle. What is the average memory access time? Ignore the impact of writes.

參考解答:$\text{AMAT} = 1 + 0.05 \times 4 + 0.02 \times 10 + 0.005 \times 100 = 1.9 \text{ clocks}$

7. [15%] The C-like pseudocode of two programs: programP and programA is shown below.

programP

main() {

int x;

x = fork();

if (x > 0) { fork(); printf("1"); }

else if (x == 0) {

printf("2");

fork();

exec("programA");

printf("3");

}

while(1);

}programA

main() {

printf("A");

while(1);

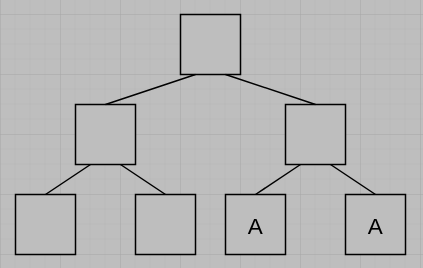

}(1) Please draw the parent-child process relationship graph resulting from the execution of the programP. Explain your answer.

(2) What is the output of the program? Explain your answer.

參考解答:

(1)

(2) 112AA

8. [15%] Assume that a process currently runs in the user mode of an x86 system. Which of the following situation(s) always cause a transition from the user mode to the kernel mode? (a) a timer interrupt occurs and the time quantum of the process has not expired, (b) a timer interrupt occurs and the time quantum of the process has expired, (c) TLB hits, (d) TLB misses, (e) the process executes a memory access instruction. Please briefly explain your answer.

參考解答:b.

9. [10%] For a memory access in a virtual memory system,

(1) is it possible that TLB hits and page fault occurs? Explain your answer.

(2) is it possible that TLB misses and page fault does not occur? Explain your answer.

參考解答:

(1) Impossible. Since all the mappings in TLB are from page table so it is not possible for TLB hit but page table miss.

(2) Possible. Since all the mappings in TLB are from page table so it is possible when mappings are in page table but not in TLB.

10. [10%] Please explain why processor affinity is considered when an operating system schedules processes in a multi-processor system.

參考解答:Some processors may already have some data in the cache of a processor and they would prefer to use that processor as a primary choice.

試題(pdf):連結

有任何問題,或想要完整解釋的,歡迎在下方留言唷!

RRO

不好意思

想請問第八題abe選項的意思

(b)感覺是一般的time out interrupt…?

(a)就不是很懂了…

(e)若要存取一個mem中的位置,不是都會先靠mmu去判斷是否合法嗎,假設用base limit來判斷,在合法存取範圍的話,就直接存取了不是嗎@@?這樣不是算純硬體的動作嗎…?

mt

系統每一個單位時間都會發出一個timer interrupt。

(a)就是假設這個process還有10個單位時間可以用,那發出timer interrupt的時候counter要-1變成9然後繼續跑。

(b)就是剛好時間用完,那就會context switch。

(e)的話你說的沒錯不應該選的,感謝!

akkk74159

請問第二題的(1)為什麼是對的呢 R type的opcode不是共用的嗎?

mt

我看了一下這題應該是問從opcode能不能看出來是R-type還是I-type,這樣的話應該就是True。